# **DIGITAL DESIGN VHDL LABORATORY NOTES**

# **CERL/EE**

# **OCTOBER 16, 1996**

VERSION 1.01

COPYRIGHT 1996 DR. CECIL ALFORD TSAI CHI HUANG CERL / EE

# TABLE OF CONTENTS

| 1. VHDL - HARDWARE DESIGN SOFTWARE APPROACH      | 6  |

|--------------------------------------------------|----|

| 1.1 INTRODUCTION                                 | 6  |

| 1.1.1 SEQUENTIAL PROGRAMMING                     | 6  |

| 1.1.2 PARALLEL PROGRAMMING                       | 6  |

| 1.1.3 OBJECT BASED PROGRAMMING                   | 8  |

| 1.1.4 PROGRAMMABLE CIRCUITS                      | 9  |

| 1.2 PROBLEMS                                     | 10 |

| 2. VHDL BEHAVIOR AND STRUCTURE MODELS            | 13 |

| 2.1 INTRODUCTION                                 | 13 |

| 2.2 PROBLEMS                                     | 18 |

| 3. STATE MACHINES AND PROGRAMMABLE LOGIC DEVICES | 19 |

| 3.1 INTRODUCTION                                 | 19 |

| 3.2 MEALY AND MOORE STATE MACHINES               | 19 |

| 3.3 VHDL PROGRAMS                                | 22 |

| 3.3.1 MEALY STATE MACHINE                        | 22 |

| 3.3.2 MOORE STATE MACHINE                        | 23 |

| <b>3.4 PROBLEMS</b>                              | 24 |

| 4. DIGITAL DEVICE MODELING                       | 26 |

| 4.1 INTRODUCTION                                 | 26 |

| 4.2 SRAM MEMORY                                  | 26 |

| 4.3 VHDL SRAM MEMORY DESIGN                      | 27 |

| 4.4 SRAM VHDL LISTING                            | 28 |

| 4.5 PROBLEMS                                     | 30 |

| 5. DIGITAL DESIGN USING DIVIDE AND CONQUER       | 32 |

| 5.1 INTRODUCTION                                 | 32 |

| 5.2 VHDL FEATURES                                | 32 |

| 5.3 ALU FUNCTIONS                                | 32 |

| 5.4 ALU COMPONENT IMPLEMENTATION EXAMPLES        | 33 |

| 5.4.1 RIPPLE CARRY ADDER IMPLEMENTATION          | 33 |

| 5.4.2 PACKAGE IARITH_PARTS_PKG LISTING           | 34 |

| 5.4.3 TESTADD. VHD LISTING                                                  | 36 |

|-----------------------------------------------------------------------------|----|

| 5.4.4 CIRCULAR SHIFTER IMPLEMENTATION                                       | 37 |

| 5.4.5 CIRCULAR SHIFT TRACE DATA                                             | 37 |

| 5.4.6 PACKAGE LOGIC_PARTS_PKG LISTING                                       | 37 |

| 5.5 ALU IMPLEMENTATION EXAMPLE                                              | 40 |

| 5.6 PROBLEMS                                                                | 42 |

| 5. ALU DATAPTH IMPLEMENTATION                                               | 43 |

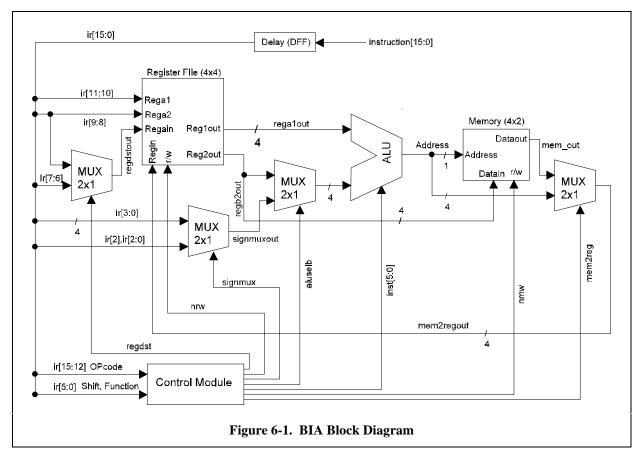

| 6.1 INTRODUCTION                                                            | 43 |

| 6.2 INSTRUCTION SET ARCHITECTURE (ISA)                                      | 43 |

| 6.3 A COMPUTER ARCHITECTURE IMPLEMENTATION                                  | 43 |

| 6.4 IMPLEMENTATION EXAMPLE                                                  | 44 |

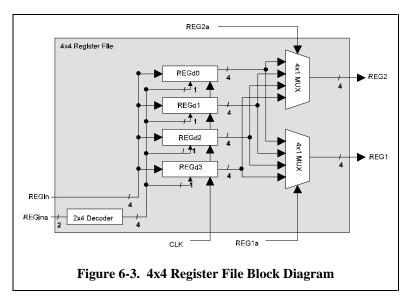

| 6.4.1 4x4 Register File and 8x4 Memory Block                                | 46 |

| 6.4.2 CONTROL MODULE                                                        | 46 |

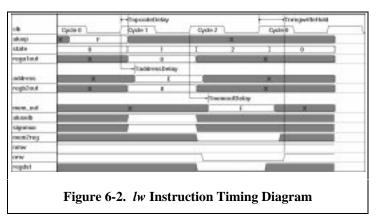

| 6.4.3 EXECUTION EXAMPLE                                                     | 47 |

| 6.4.4 VHDL LISTING                                                          | 50 |

| 6.4.4.1 regf4x4.vhd                                                         | 50 |

| 6.4.4.2 mem4x2.vhd                                                          | 52 |

| 6.4.4.3 ctrlm.vhd                                                           | 54 |

| 6.4.4 BIA.vhd                                                               | 59 |

| 6.5 PROBLEMS                                                                | 59 |

| 7. APPENDICES                                                               | 60 |

| 7.1 INSTALL WARP ON PC                                                      | 60 |

| 7.1 INSTALL WARP ON FC<br>7.2 INTRODUCTION TO WARP4 VHDL DEVELOPMENT SYSTEM | 60 |

| 1.4 INTRODUCTION TO WART 4 VIIDL DEVELOPMENT SISTEM                         | U  |

## LIST OF FIGURES

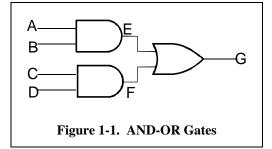

| Figure 1-1. AND-OR Gates                              | 7  |

|-------------------------------------------------------|----|

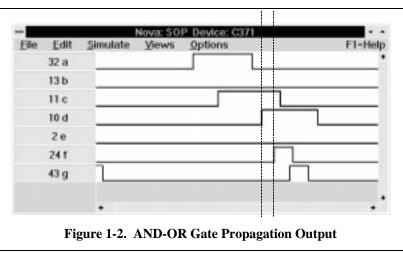

| Figure 1-2. AND-OR Gate Propagation Output            |    |

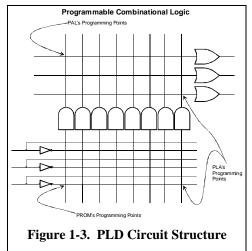

| Figure 1-3. PLD Circuit Structure                     | 10 |

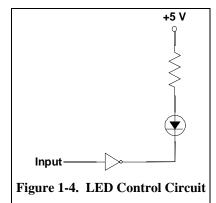

| Figure 1-4. LED Control Circuit                       | 10 |

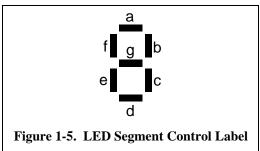

| Figure 1-5. LED Segment Control Label                 | 11 |

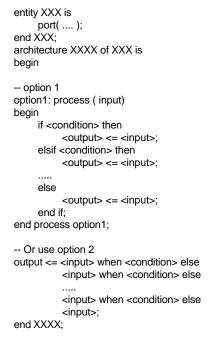

| Figure 2-1. Example of Discrete Components            | 13 |

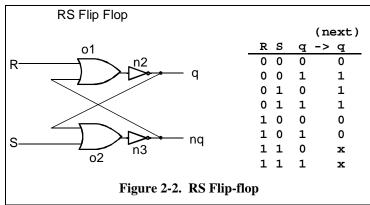

| Figure 2-2. RS Flip-flop                              | 14 |

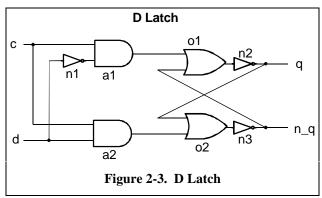

| Figure 2-3. D Latch                                   | 14 |

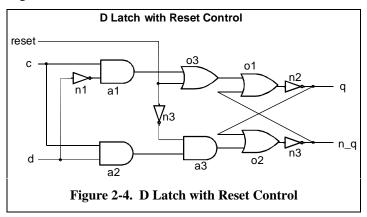

| Figure 2-4. D Latch with Reset Control                | 14 |

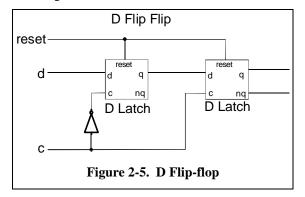

|                                                       | 15 |

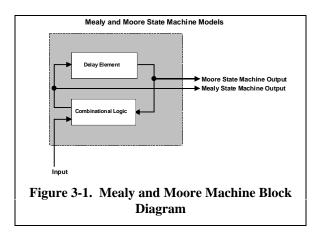

| Figure 3-1. Mealy and Moore Machine Block Diagram     | 19 |

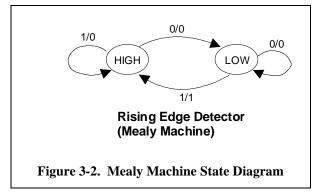

| Figure 3-2. Mealy Machine State Diagram               |    |

| Figure 3-3. Mealy Machine Timing Diagram              | 20 |

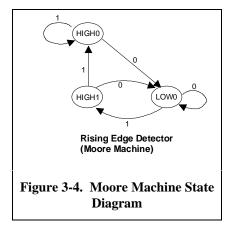

| Figure 3-4. Moore Machine State Diagram               | 21 |

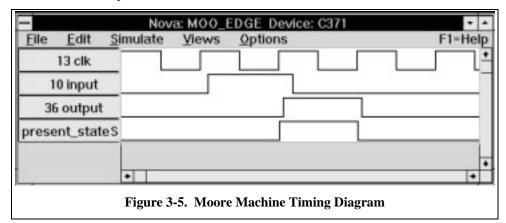

| Figure 3-5. Moore Machine Timing Diagram              |    |

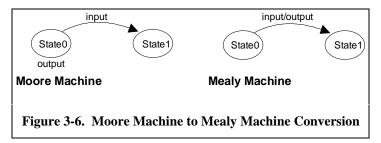

| Figure 3-6. Moore Machine to Mealy Machine Conversion | 22 |

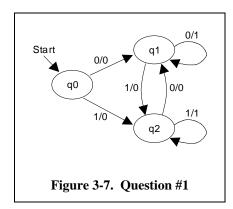

| Figure 3-7. Question #1                               | 24 |

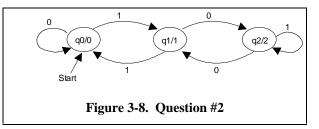

| Figure 3-8. Question #2                               | 24 |

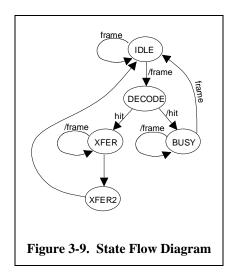

| Figure 3-9. State Flow Diagram                        | 25 |

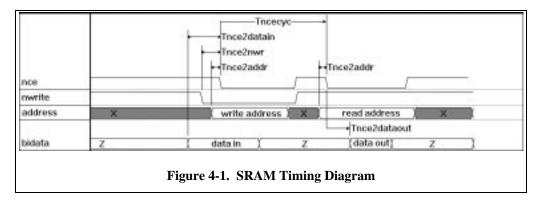

| Figure 4-1. SRAM Timing Diagram                       | 27 |

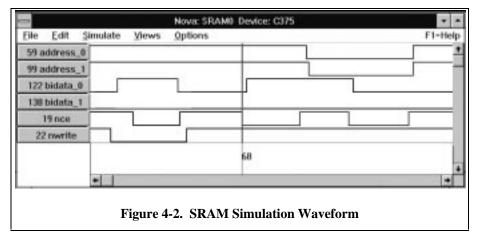

| Figure 4-2. SRAM Simulation Waveform                  | 27 |

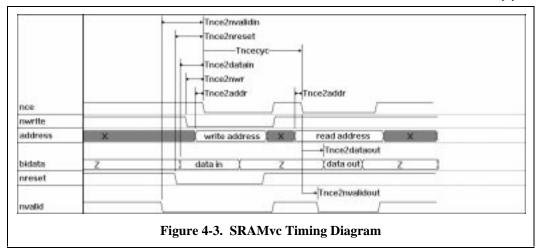

| Figure 4-3. SRAMvc Timing Diagram                     | 31 |

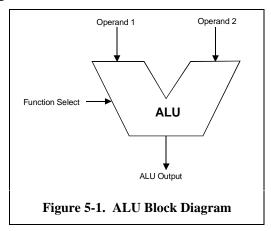

| Figure 5-1. ALU Block Diagram                         |    |

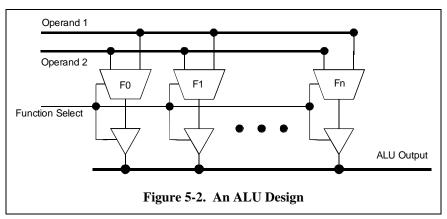

| Figure 5-2. An ALU Design                             | 33 |

| Figure 5-3. Ripple Carry Adder Waveform               |    |

| Figure 6-1. BIA Block Diagram                         |    |

| Figure 6-2. lw Instruction Timing Diagram             |    |

| Figure 6-3. 4x4 Register File Block Diagram           | 46 |

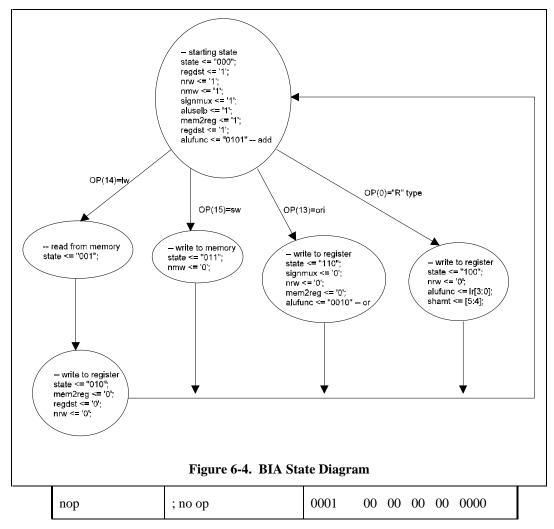

| Figure 6-4. BIA State Diagram                         |    |

| Figure 6-5. BIA Simulation Timing                     |    |

| Figure 7-1. Project Window                            | 60 |

| Figure 7-2. Device Window                             | 61 |

## LIST OF VHDL CODE

| Listing 1-1. Simple VHDL Code for Dataflow Modeling        | 7  |

|------------------------------------------------------------|----|

| Listing 1-2. Digital Design Goodness Criteria              | 9  |

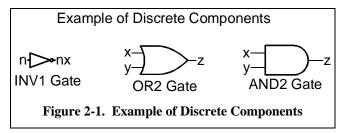

| Listing 1-3. Example VHDL Code                             | 11 |

| Listing 2-1. Dataflow Modeling of AND2, OR2 and INV1 Gates | 16 |

| Listing 2-2. D Latch Structure Modeling                    | 16 |

| Listing 2-3. D Latch Behavior Modeling                     | 17 |

| Listing 2-4. D Flip Flop Behavior Modeling                 | 18 |

| Listing 3-1. Mealy Machine VHDL Code                       | 23 |

| Listing 3-2. Moore Machine VHDL Code                       | 24 |

| Listing 4-1. SRAM VHDL Code                                | 30 |

| Listing 5-1. Iarith_parts_pkg VHDL Code Listing            | 36 |

| Listing 5-2. Testadd.vhd VHDL Code Listing                 | 36 |

| Listing 5-3. Circular Shift Trace Listing                  | 37 |

| Listing 5-4. Logic_parts_pkg VHDL Code Listing             | 39 |

| Listing 5-5. Example ALU VHDL Code Listing                 | 42 |

| Listing 6-1. Regf4x4.vhd VHDL Code                         | 52 |

| Listing 6-2. Mem4x2.vhd VHDL Code                          | 54 |

| Listing 6-3. Ctrlm.h VHDL Code                             | 59 |

|                                                            |    |

## 1. VHDL - Hardware Design Software Approach

## 1.1 Introduction

Software programming, no doubt, is a common skill required by all college engineering students. Such knowledge is indispensable for utilizing a computer as a tool for achieving greater engineering goals in both the classroom and the real world. Programming tasks for applications range vary in level of detail and complexity. The readability of programming language constructs span from a very low level, which is almost at the hardware level such as PAL programming, to a high level such as application level programming. Good examples of application programming are database, UNIX shell scripts, DOS batch file, and SPICE circuit simulation. Almost all programming language lie between these two ends. The major difference between programming languages is their programming complexity which affects such things as development time. Sequential programming is most common among programming languages. Examples of sequential languages are BASIC, FORTRAN, Pascal and C. Besides sequential programming, there are other programming paradigms: parallel programming and object based programming. These paradigms are new for most people, and they will be introduced during the process of learning VHDL. VHDL is not much different from conventional programming languages, except it uses sequential, parallel, and object based software paradigms to achieve its goal: namely, digital hardware simulation and synthesis. In other words, a VHDL program is used to specify, to model, and to "create" digital hardware.

VHDL stands for VHSIC (Very High Speed Integrated Circuit) Descriptive Language. VHDL is promoted by the Department of Defense (DOD) mainly to facilitate the standardization of all digital hardware design. VHDL serves as a documentation tool at the beginning to describe a system in a unified manner across the cooperative group of a project. VHDL was started in early 1980 inside of DOD and eventually got standardized by IEEE with the name standard 1076 (IEEE-STD-1076) in 1987. Although further enhancements have been added to the later version of VHDL, for example standard 1164 (IEEE-STD-1164), standard 1076 will be sufficient to learn and explore most of the language feature.

## 1.1.1 Sequential Programming

This type of programming is characterized by the sequential nature of program flow. Popular programming languages such as Pascal, C, BASIC and FORTRAN are the examples in this category. It is also called imperative programming because programming statements to be executed are imperative. Programs are executed in sequential order and a statement is executed following the statement that precedes it in the proogramm. There is always a clear decision as far as which the next program statement is to be executed next. In summary, in sequential programming, there is no ambiguity as far as the statements execution order is concerned.

In VHDL syntax, the statements after the reserved keyword *process* or within the *process* block will be executed in sequential order. Typical VHDL sequential statements are condition statements, loop statements, and assignment statements. The syntax of each type of statement can be found in any reasonably thorough VHDL tutorial text book.

### **1.1.2 Parallel Programming**

The parallel programming concept is a more difficult programming paradigm to grasp for people used to sequential programming. The parallel programming concept is straightforward and is expressed through

its name; statements are executed in parallel. Moreover, the process of executing statements in parallel mimics the real world phenomena and thus coincide better with the behavior of digital circuits. In parallel processing, the application of parallel programmingg, programs executed in parallel have the advantage of boosting program execution speed versus the equivalent sequential program. In the area of VHDL programming, the goal is to mimic the physical digital system. Due to the fact that hardware operates executed in parallel, to capture the functionality of the hardware, it is important for VHDL to have the features to facilitate the modeling of such behavior.

Parallel program statements, as the name suggests, are the statements that can be executed in parallel. Parallel statements are less intuitive to use due to their nondeterministic nature. Ideally, all parallel statements should be executed at the same time. However, in the popular Von Neumann machine or sequential computer world (eg., PCs and worstations), only sequential statements can be directly executed. Therefore, parallel programming must be simulated on a sequential machine. When simulating parallel statements, due to the fact that statements are executed in parallel and random order, it is crucial that the execution order be irrelevant and not affect the result.

An example of a parallel system is shown in Figure 1-1. It describes a digital hardware circuit where four inputs and one output are involved. Inputs A, B, C and D are fed into two AND gates, and the outputs of these AND gates, E and F, are then fed into an OR gate whose output is shown below(see Figure 1-1).

A piece of simple VHDL code shown in Listing 1-1 describes the circuit above. Notice the section after *dataflow\_machine architecture* in the code. Three statements, a, *b*, and *c* describe AND and OR logical assignments. These statements can be rearranged in any order, and the simulated output G should still be the same.

```

-- Sum of product example

entity sop is

port ( a, b, c, d: in bit;

e, f: inout bit;

g: out bit);

end sop;

architecture dataflow_machine of sop is

begin

-- Begin parallel statements

g <= e or f; -- Statement a

e <= a and b; -- Statement b

f <= c and d; -- Statement c</li>

```

Listing 1-1. Simple VHDL Code for Dataflow Modeling

The result G will be the same if the statements assigning E, F and G outputs were placed in any order. Any data arriving at the inputs A, B, C, and D will pass through the AND and OR gates in continuous time fashion. Whatever shown up at A, B, C or D inputs will be reflected at the intermediate outputs E and F and at the final output G. Thus, output G should change instantly according to the essence of parallel programming. In the world of hardware execution, there is always a delay when data pass through gates. The VHDL code of hardware synthesis is mapped into a Cypress CPLD 375 device and fitted with optimization disabled. The simulation of the mapped Cypress 375 PCLD shows that there is a delay of about 5 ticks between each logical gate. Notice that ticks from VHDL simulation below do not represent any real-time. Instead, a simulation tick is simply a unit of delay of simulation time. In the real world, gates delay are on the order of nanoseconds  $(10^{-9} \text{ sec})$ .

Intuitively, the parallel VHDL statements above should be executed in the order: c, a and b. However, the hardware VHDL simulator handles the situation differently. The VHDL simulator executes the parallel statements in clock random order fashion.

Notice that VHDL statements written within the *process* block have been executed sequentially. Therefore, all VHDL statements outside of the *process* block will be executed in parallel. For example, two *process* blocks can be executed in parallel. To resolve sequential statements inside of each *process* block, VHDL uses the concept of delta time slots for each clock tick. In each clock tick, the simulator allocates however many sub-ticks called delta for simulating the instantaneous statement execution. Individual parallel statement are being executed at delta ticks. A simulated clock tick will only move forward when the delta tick yields consistent outputs. An example above would be stable E, F, and G outputs.

## 1.1.3 Object Based Programming

Objected based programming is different from the sequential and parallel paradigms. It should be treated more like a methodology than a paradigm. Objected based methodology basically enforces structure into VHDL. This facilitates the systematic construction of large and complicate digital system. Object based programming also supports the concept of abstract data types enabling the VHDL engineer to construct custom data types and operations and then to store them systematically for future VHDL projects. This is the concept of VHDL code reuse. Since the feature of breaking VHDL code into small components and libraries is already built into the language, it provides the VHDL designer with the structural divide and conquer technique when building larger systems. Moreover, the concept of code reuse definitely saves

system development time. In summary, object based features are extremely useful for VHDL code development, management, and reusability.

## **1.1.4 Programmable Circuits**

Digital design technology has evolved greatly in recent years. This can be seen in the field of ever changing microprocessor design where complexity and performance double every year. With improvements to digital hardware technology, the criteria used to determine a design's goodness remain

| Correctness   | Ability to exactly perform their tasks, as defined by the requirement and specification. |

|---------------|------------------------------------------------------------------------------------------|

| Robustness    | Ability to function even in abnormal conditions.                                         |

| Extendibility | Ability to ease change in specification change.                                          |

| Reusability   | Ability to be reused, in whole or in part, for new applications.                         |

| Compatibility | Ability to combine with others.                                                          |

|               | Listing 1-2. Digital Design Goodness Criteria                                            |

the same, and they are listed in Listing 1-2.

These five criteria are borrowed from the book, *Object-oriented Software Construction*, by Bertrand Meyer. Although, they were used to describe software quality, the concepts are also appropriate to be used on hardware. Notice that hardware design technical merits such as speed and cost are not mentioned because they highly depend on the state of technology and market demand.

The word, flexibility, sums up all these criteria above. The practice of digital design nowadays must be flexible. Thus, the trend is to replace ridged discrete logic component with programmable devices to maximize hardware flexibility.

Traditional programmable circuits comes in three flavors of simple combinational logic circuit: Programmable Read Only Memory(PROM), Programmable Logic Array(PLA), and Programmable Array Logic(PAL). All these three devices contain similar hardware structure of AND and OR arrays. Input goes from the AND array to the OR array. The difference is that PROM contains fixed AND and programmable OR arrays, PAL contains programmable AND and fixed OR arrays, and PLA contains programmable AND and OR arrays. (See the figure Figure 1-3.)

Most of the time, a digital hardware designer doesn't need to know the circuit structure of the programmable logic device (PLD) that he is using except he is conscious about the design's speed and capacity. For example, he might want to try to "fit" a large piece of circuit into a given PLD or to select a type of fast PLD to meet a timing limit. Digital hardware can be programmed to fit a circuit into a PLD using hardware programming languages such as CUPL, Abel, PALism, and VHDL.

For more complex PLDs (CPLDs), memory elements such as flip flop devices are involved and they will be introduced later.

### 1.2 Problems

Binary Coded Decimal (BCD) is a useful decimal number representation using binary numbers. Many times, it is the only representation that digital hardware uses to communicate with humans since humans are custom to the decimal numbering system. One example is to use BCD to control the decimal LED display panel of a calculator. Each LED decimal digit has eight segments and each segment contains an LED source as shown in Figure 1-4.

At high input "1", current flows through the LED and resistor, and the LED glows. The typical current is about 20mA, and voltage drops 1.6 Volts(V) across the LED and 3 V across the resistor. If input is low "0", no current will flow through LED and it will become dim.

The LED segment specification is illustrated in Figure 1-5.

The input consists of 5 bits, and the output consists of 7 bits. Out of 5 input bits, 4 bits are used to specify binary value, and one bit is used to blank all LED segments. For all output bits, one bit is used for controlling each of the segment, and one bit is used to indicate overflow of the input binary number, for example binary input greater than 9. The LED logic specification is shown in Table 1-1.

An LED segment control decoder is used to control a one-digit LED display panel. Construct such a decoder using VHDL. This can be done using *if* statements nested inside of a *process* statement or *when* statements alone. The form of such decoder could look like the VHDL code segment in Listing 1-3.

Listing 1-3. Example VHDL Code

After completing the implementation, test the decoder for various inputs and simulate the resulting output using the NOVA simulator. The simulation session can be saved into the trace file with the "PSD" extension. This is done by using the mouse to select *FILE* and then *Write Trace* (\*.*PSD*) on the top of the NOVA menu bar. In the saved PSD file, annotate the clock tick that corresponds to the decoder action. For example, the input that leads to the output display.

| INPUT |

|-------|

|-------|

OUTPUT

| Comment | Blank | in1 | in2 | in3 | in4 | Overflow | а | b | С | d | е | f | g |

|---------|-------|-----|-----|-----|-----|----------|---|---|---|---|---|---|---|

| Blank   | 1     | х   | х   | х   | х   | 0        | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0       | 0     | 0   | 0   | 0   | 0   | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1       | 0     | 0   | 0   | 0   | 1   | 0        | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 2       | 0     | 0   | 0   | 1   | 0   | 0        | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 3       | 0     | 0   | 0   | 1   | 1   | 0        | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 4       | 0     | 0   | 1   | 0   | 0   | 0        | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 5       | 0     | 0   | 1   | 0   | 1   | 0        | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 6       | 0     | 0   | 1   | 1   | 0   | 0        | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 7       | 0     | 0   | 1   | 1   | 1   | 0        | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 8       | 0     | 1   | 0   | 0   | 0   | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 9       | 0     | 1   | 0   | 0   | 1   | 0        | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| а       | 0     | 1   | 0   | 1   | 0   | 1        | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| b       | 0     | 1   | 0   | 1   | 1   | 1        | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| С       | 0     | 1   | 1   | 0   | 0   | 1        | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| d       | 0     | 1   | 1   | 0   | 1   | 1        | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| е       | 0     | 1   | 1   | 1   | 0   | 1        | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| f       | 0     | 1   | 1   | 1   | 1   | 1        | 0 | 1 | 1 | 1 | 0 | 0 | 0 |

Table 1-1.

LED-Control Truth Table

## 2. VHDL Behavior and Structure models

## 2.1 Introduction

The ability to "remember" is important in the field of digital systems. The digital memory element is a necessary and fundamental block for building complex digital systems. Despite its importance, it takes no more than basic digital logic for its construction. There are many ways to construct a digital memory element using basic logic gates such as NOT, AND, and OR.

There are three ways to model a digital system using VHDL. A piece of VHDL hardware can be modeled in structural, data flow and behavior methodologies. In this lesson, methods of building memory elements such as latches and flip flops are studied using both single and mixed methodologies.

A natural way to describe discrete components is to use a data flow model. Discrete gates such as a one input and one output NOT gate, INV1, two inputs and one output AND gate, AND2, and two inputs and one output OR gate, OR2, can be modeled fairly easily, and they are illustrated in Figure 2-1. The logic gates in Figure 2-1 have their inputs and outputs labeled. These components will be used to illustrate more examples of elaborate logic devices, such as a digital memory element.

There are many types of memory elements that one can create using the basic gates shown in Figure 2-1. A simple memory block that one can make is an RS flip flop which uses two OR2 and INV1 gates. For the sake of consistency with the previous example, NOR2 is not included for now. Even though OR2 is used to create an RS flip flop, DeMorgan's law would also permit AND2 to be used as well.

Notice the flip flop is named RS because the flip and flop can be set (output=1) or reset (output=0) depending on the inputs (R and S). When both R and S inputs are set to zero, outputs (q and nq) will be suspended to the previous values of R and S. Be aware that both R and S, at the same time, can't be set to one for two reasons. The first reason is that once R and S become one, output q and nq will no longer be complementary to each other. Both q and nq will become zero, and this violates the assumption of complementing flip flop output. Second, once the output q and nq become zero, the next state after R and S change, outputs q and nq are impossible to predict due to the feedback of q and nq values. See Figure 2-2 for the RS flip flop logic truth table.

Although an RS flip flop is easy to implement, it is not an ideal memory device due to its incomplete input states. From the perspective of a digital designer, it is cumbersome to guarantee the partial input state. A better way to use the same memory block is to modify the RS flip flop to take care of the partial input problem. One simple solution is to add two AND2 gates at the front of RS flip flop to prevent R and S from becoming one at the same time. The resulting circuitry is called a D latch. See Figure 2-3 for this modified memory element.

A D latch functions very similar to an RS flip flop because it remembers past states. However, it works differently because output is triggered by the level of the input signal instead of the input signal edge. As a matter of fact, a flip flop works differently from a latch because the flip flop output signal is triggered at the clock edge and the latch output signal is triggered at the level of clock signal.

Digital circuitry during the beginning of operation, especially memory elements, will go to erroneous states unless provision is made for startup operation. At the initial stage of the memory operation, the value stored inside of the memory element is unknown, and, if this unknown is to be applied to rest of the system, the system will almost be guaranteed to produce error. The modification to D latch is shown in Figure 2-4. The new latch get reset circuitry so the internal value stored can be set to zero (low) whenever the reset signal goes high.

although the difference between flip flops and latches have been discussed, it is important to note the application side of these memory elements. In the world of digital design, the majority of digital system is

running synchronously with the system clock. Since flip flops activate at an instance in time to acquire data, relatively speaking, flip flops are more useful than latches because the output of flip flops is held constant for a full clock cycle instead of half a clock cycle.

Cascading two D latches can produce a D flip flop. The clock signal that runs through these two latches is inverted so data can pass through the latches in pipeline fashion. Due to the holding of input data at the lower phase clock signal, input signal of the first latch is preserved for the instance when the clock signal goes down. Simultaneously, the signal output from the first latch is acquired by the second latch, and the signal is held constant until the second latch's clock goes down. A D flip flop drawing made by cascading two D latches is shown below in Figure 2-5.

Now the memory basics have been explained, and it is time to model some of the memory block using VHDL. The difference between structure, dataflow, and behavior models will be shown in later examples. For example, in Listing 2-1, each discrete logic component, AND2, OR2 and INV1, is defined at the beginning using the dataflow model as state before. Notice that VHDL programming structure is declared with *entity* statement first and followed by an *architecture* statement. Signals defined in the *entity* block under the keyword *port* are visible inside of the architecture block.

```

-- INV1 Gate

entity inv1 is

x: in bit:

port(

nx: out bit);

end inv1;

architecture behav of inv1 is

begin

nx \leq not x;

end behav;

--AND2 Gate

entity and2 is

port(

x, y: in bit;

z: out bit);

end and2;

architecture behav of and2 is

begin

z \leq x and y;

end behav;

-- OR2 Gate

entity or2 is

port(

x, y: in bit;

z: out bit);

end or2:

```

#### Listing 2-1. Dataflow Modeling of AND2, OR2 and INV1 Gates

As its name implies, structures modeling uses the gates defined above to connect to others to make into a system. The process of describing the system structure in gate connection is shown in Listing 2-2. The VHDL code after the gate definitions shown in Listing 2-1 shows how to connect gates, and this is done through the use of VHDL statement *map*.

```

-- structure modeling of D latch

entity lat_ds1 is

port(

c, d: in bit; -- input data

q, nq: inout bit);

end lat_ds1;

architecture struct of lat_ds1 is

signal i1_nx: bit;

signal i2_nx: bit;

signal i3_nx: bit;

signal a1_z: bit;

signal a2_z: bit;

signal o1_z: bit;

signal o2_z: bit;

component and2

port(x, y: in bit; z: out bit);

end component;

component or2

port(x, y: in bit; z: out bit);

end component;

component inv1

port(x: in bit; nx: out bit);

end component;

begin

-- structure connection

a1: and2 port map(c, i1_nx, a1_z);

a2: and2 port map(c, d, a2_z);

o1: or2 port map(a1_z, nq, o1_z);

o2: or2 port map(a2_z, q, o2_z);

i1: inv1 port map(d, i1_nx);

i2: inv1 port map(o1_z, q);

i3: inv1 port map(o2_z, nq);

end struct;

```

Listing 2-2. D Latch Structure Modeling

The variables inside of the mapping statements are declared after the D latch architecture declaration, *architecture struct of lat\_ds1 is*, and before the *begin* statement. These signals can only be used here, and they are not accessible by other architecture code blocks.

Gate components used here are also required to be declared. The declaration of a component is similar to C, FORTRAN or Pascal programming where all procedures or subroutines are required to be declared before use. However, it is not exactly the same as doing programming because each component declared could be physical part rather than a conceptual abstract. For example, the ports declared by component do have corresponding physical meaning, namely wires to carry signals. This concept should be understood from the digital hardware engineer perspective.

Now, consider taking the same D latch circuit and describing or modeling it behaviorally in VHDL. This code is shown in Listing 2-3. As we have noticed, the VHDL code here is shorter than its corresponding structure model because the circuit behavior is directly described. It is a higher level modeling, and it can be done easily if the designer knows exactly how his circuit behaves. Many times, the digital circuit designer knows how the circuit should behave but is not sure if the actual circuit behaves as he predicts. Therefore, it is useful to construct the circuit as a structure model and verifies its working order. Behavior modeling saves time and it is based on the assumption that the designer knows his circuit's behavior well. If the assumption about the circuit is wrong, then behavior modeling can lead to a disastrous result. Remember, behavior modeling should be used as much as possible when modeling digital circuits because it will save much development time.

In the field of VLSI design, the translation of a behavior model to a structure model is called *hardware synthesis*, and it relies much on the software intelligence. During the process of mapping a VHDL circuit to the actual hardware, it is best to specify as much structure as possible if the speed and the size requirement of the circuit are a concern. As an analogy, think of a programmer who wants his code to be as fast and efficient as possible. The programmr does better write the code in assembly (or even better - machine language) instead of relying on a the high level language compiler. For the exercises here, problems mainly focus on translating VHDL code to hardware. In other words, VHDL will be used as a programming language to map into hardware. Again, remember the concept of *hardware synthesis*. In *hardware synthesis*, the digital designer needs to be conscious of the final form of the mapped circuit.

```

-- behavior modeling of D latch

entity lat db1 is

port(

c, d: in bit;

-- input data

q, nq: inout bit

):

end lat db1;

architecture behavior of lat_db1 is

begin

-- behavior model

behavior: process (c)

begin

if c='1' then

<= q.

q

nq

<= not d;

end if

end process behavior;

end behavior;

```

Another example of behavior modeling is again the D flip flop construction using two D latches which was illustrated earlier in Figure 2-5. Listing 2-4, however, shows the construction of a D flip flop without using any D latches. By using the behavior modeling technique, the VHDL code length was reduced drastically. A circuit similar to a D flip flop in size would be tedious to describe totally described in a structural model.

```

-- behavior modeling of D latch

entity rdffb is

port(

-- reset signal

reset: in bit;

-- input data, c=clock, d=data

c, d: in bit;

q, nq: out bit ); -- output q and not q

end rdffb;

-- behavior model

architecture behavior of rdffb is

begin

behavior: process (c, reset)

begin

if reset='1' then

<= '0'

q

ng <= '1';

elsif (c='1' and c'event) then

q <= d;

nq

<= not d;

end if:

end process behavior;

end behavior:

```

Listing 2-4. D Flip Flop Behavior Modeling

## 2.2 Problems

- Implement a D latch with reset using VHDL structure modeling. Demonstrate its functionality in the Cypress NOVA simulator by resetting the circuit, latching in a high value, and resetting again at the next clock cycle when the input is kept high. Save the simulation session to a stimulus file (\*.SIM) and trace file (\*.PSD) using the NOVA FILE menu items.

- 2) A T flip flop can be defined as a flip flop that toggles the output at the edge of the clock cycle, for example, rising or falling edge. Implement T flip flop behaviorally. Again, save the simulation session in both stimulus file and trace file.

- 3) Implement an RS flip flop using an AND gate, and model it structurally. Demonstrate and show its functionality.

- 4) In VHDL, implement the circuit described below using two D flip flops with /RESET input. The circuit should first be implemented in a behavior model and, then, in a structure model. Show the functionality using the VHDL simulator. (Hint: Utilize /RESET input).

```

INPUT:

Two input lines, A and B.

OUTPUT:

One output C.

CONDITIONS:

a) The output goes to 1 on every positive transition of the A line.

b) The output goes to 0 on every positive transition of the B line.

c) The output must be capable of set to 1 again after it being to 0.

d) Input B takes precedence over Input A to affect the output.

```

## 3. State Machines and Programmable Logic Devices

## 3.1 Introduction

Simple programmable devices that we saw earlier can be extended into state machine by a combining memory elements (such as latches and flip flops) with combinational logic elements such as an AND-OR array. A classical example of constructing state machine uses a PROM and latches. Although the construction is simple, the design lacks flexibility for testing. In addition, the use of discrete PROM and latches for creating state machine suffers performance loss due to the hardware interconnection overhead. Modern state machine construction uses programmable devices such as PLDs that integrate memory and discrete elements into one block of hardware real-estate.

## 3.2 Mealy and Moore State Machines

There are two classical state machine constructions, and they are described in most of the digital design textbooks. They are Mealy and Moore state machines. It can be seen from Figure 3-1 that both state machines are very similar. The Moore machine uses only the output of a delay element to generate the system output whereas the Mealy machine uses both the system input and a delay element output for system output. In theory, both machines are equivalent, so one can convert a synchronized digital hardware design from a Mealy to a Moore state machines or vice versa. Such a statement is not true in the real world of digital design. The Moore state machine generates output based only on its current state. Therefore, the Moore machine output is usually synchronized with the system clock or the clock edge of the output D flip flop (the delay element). In the Mealy machine, because output depends on both the input and current state, output will change whenever the input changes. In other words, in the Mealy system, when output is released at a clock edge, the input is usually latched and considered prior to the release of latched output.

The Mealy machine is more difficult to understand than the Moore machine. Because the Mealy machine outputs based on the input and the current state, the correct initiating output process in a Mealy machine is first to change the input value. Due to the dependency of input and the current state, Mealy machine output changes next. However, the change at the input will also trigger the change at the machine state. At last, the output will change again due the new state. Notice that Mealy machine output only at the edge of the state transition, see Figure 3-3. whereas the Moore machine output coincide with the state change, see Figure 3-5.

An VHDL example of a rising edge detector will be constructed using both machines. First, the state diagram of such device as a Mealy machine is shown in Figure 3-2.

There are two states in the state machine: HIGH and LOW. Notation x/y next to an arc between states stands for input/output values during the state transition. The machine advances to the next state when it sees an input x. In mean time, the machine also outputs y. The VHDL code for the state machine shown in Figure 3-2 is listed in Listing 3-1.

Listing 3-1 contains the usual VHDL components such as *entity*, *architecture* declaration and the VHDL body. A *type* statement after the *architecture* declaration declares the enumerated type *StateType*. It is advantageous to use VHDL enumerated type so each state of the state machine can have meaningful name (for example, HIGH and LOW). Two signal identifiers *present\_state* and *next\_state* are declared and used like any identifiers, except they can only be assigned an enuerated state value, HIGH or LOW. The use of the identifiers *present\_state* and *next\_state* and *next\_state* and *next\_state*, *state\_machine*, *state\_clocking*, and *mealy\_output* process statements. These blocks of the VHDL program execute their statements in parallel. In particular, depending on the input, *state\_machine* controls the state to which to advance. *Mealy\_output* generates output depending on the current state and input. *State\_clocking* dictates the synchronization between the state machine and clock rising edge. The timing diagram is shown in Figure 3-3. This figure shows that input triggers output instantly and that present\_state does not change its value until the beginning of the next rising clock edge. Thus the timing diagram, Mealy machine timing diagram, agrees with which statement stated above where outputs at the state transition of clock rising edges. In addition, it also shows that Mealy machine output is not registered and the machine will reflect whatever input value it sees on its output.

| -                   |         | Nova: I |         | Device: C3 | 71       |            | * *     |

|---------------------|---------|---------|---------|------------|----------|------------|---------|

| <u>Eile Edit Si</u> | imulate | Views   | Options |            |          |            | F1-Help |

| 13 clk              |         |         |         |            |          |            | f       |

| 10 input            | 2.2.2   | 0.00    |         |            | - 60 - F | 44 - 193 - |         |

| 2 output            | 8       |         |         | 2.0        |          |            |         |

| present_stateS      |         |         |         |            |          |            |         |

|                     |         |         |         |            |          |            |         |

|                     |         |         |         |            |          |            | -       |

|                     | +       |         |         |            |          |            | +       |

Given a Mealy machine, it is possible to convert it to an equivalent Moore machine using a deterministic algorithm. With the differences of Mealy and Moore machines in mind, the algorithm consists of the following steps:

- Put the state machine diagram of edge detector in Figure 3-2 into table form, as shown in Table 3-1. Realize that the table entry is constructed based on state transitions. Because there are four transitions, four table entries (four columns) are shown.

- 2) Combine the last two rows of table entries, output state and output value, to form new Moore machine states. According to the table, three unique states result: HIGH0, HIGH1, and LOW0.

| Entry #      | 1    | 2    | 3   | 4    |

|--------------|------|------|-----|------|

| Input State  | HIGH | LOW  | LOW | HIGH |

| Input Value  | 1    | 1    | 0   | 0    |

| Output State | HIGH | HIGH | LOW | LOW  |

| Output Value | 0    | 1    | 0   | 0    |

Table 3-1.

3) Create the new Moore machine state table from Table 3-1 using the new states. For example, the Mealy state machine transition table entry column 1 contains four values: input state, input value, output state, and output value. As shown before, output state and output value are used to generate the corresponding Moore machine state, HIGH0. Input state and input value are to be used to generate the corresponding Moore machine state transitions. Here, Mealy input state HIGH is replaced by the Moore state HIGH0 and HIGH1 (HIGH plus all possible outputs). Now, two corresponding Moore state transitions are derived; HIGH0 and input 1 goes to HIGH0, HIGH1 and input 1 goes to HIGH0. The same process applies to the other entry columns (2, 3, and 4), see Table 3-2.

**Table 3-2.**

| Moore States | Input 0 | Input 1 | Output Value |

|--------------|---------|---------|--------------|

| LOW0         | LOW0    | HIGH1   | 0            |

| HIGH0        | LOW0    | HIGH0   | 0            |

| HIGH1        | LOW0    | HIGH0   | 1            |

4) Make a Moore machine state diagram based on this state transition table, as shown in Figure 3-4.

5) Describe the Moore machine in VHDL constructs, as shown in Listing 3-2.

6) Express the Moore machine operation in the form of a timing diagram. The timing Diagram of the derived Moore machine is shown in Figure 3-5. In the figure, the output signal coincides with the state transition, as is expected from a Moore state machine.

The inverse process of converting a Moore state machine to a Mealy state machine is simpler. The steps are rather trivial and consist of changing every state output in the Moore machine to the out going transition output of the corresponding Mealy machine. This process effectively converts a machine from a state output state machine to a transition output state machine. See Figure 3-6.

When selecting Mealy versus Moore state machine types for a design, one needs to keep in mind the advantages and disadvantages of each construction. For a Mealy machine, system equations are intuitive to derive because input is readily available. Due to its simplicity, a Mealy machine contains fewer memory elements than a Moore machine. However, because of input dependency, Mealy output also depend highly on the input. For slow input, this phenomenon can translate into a performance bottleneck. Moore machine, on the other hand, does not suffer such input dependency since it "buffers" the system input. However, the tradeoff will be that Moore machine needs more hardware to construct.

## 3.3 VHDL Programs

### 3.3.1 Mealy State Machine

| entity mea_edge is port (<br>reset, clk, input: in bit;<br>output: inout bit;<br>mea_output: out bit );<br>end mea_edge; |  |

|--------------------------------------------------------------------------------------------------------------------------|--|

| architecture mealy_machine of mea_edge is                                                                                |  |

| type StateType is (LOW, HIGH);<br>signal present_state, next_state: StateType;                                           |  |

| begin                                                                                                                    |  |

```

state_machine: process(present_state) begin

case present_state is

when LOW => if (input='0') then

next_state

<= LOW;

else

next_state <= HIGH;

end if;

when HIGH => if (input='0') then

next_state

\leq LOW;

else

next_state

<= HIGH;

end if;

end case;

end process state_machine;

state_clocking: process(clk) begin

if (clk'event and clk='1') then

present_state <= next_state;

mea_output <= output;

end if;

end process state_clocking;

mealy_output: process(input, present_state) begin

if (present_state=LOW and input='1') then

output \leq 1';

else

output <= '0';

end if;

end process mealy_output;

```

end mealy\_machine;

#### Listing 3-1. Mealy Machine VHDL Code

#### 3.3.2 Moore State Machine

entity moo\_edge is port ( reset, clk, input: in bit; output: out bit ); end moo\_edge;

architecture moore\_machine of moo\_edge is

type StateType is (LOW, HIGH0, HIGH1); signal present\_state, next\_state: StateType;

begin

state\_machine: process(present\_state) begin

```

case present_state is

when LOW => if (input='0') then

next_state <= LOW;

else

next_state <= HIGH1;

end if;

when HIGH0=> if (input='0') then

next_state

<= LOW;

else

<= HIGH1;

next_state

end if;

when HIGH1 => if (input='0') then

next_state

<= LOW;

else

next_state

<= HIGH0;

end if;

end case;

end process state_machine;

```

```

state_clocking: process(Clk) begin

if (clk'event and clk='1') then

present_state <= next_state;

end if;

end process state_clocking;

moore_output: process(present_state) begin

if (present_state=HIGH1) then

output <= '1';

else

output <= '0';

end if;

end process moore_output;

end moore_machine;

Listing 3-2. Moore Machine VHDL Code</pre>

```

## **3.4 Problems**

1) Convert the Moore machine in Figure 3-7 into a Mealy machine. Implement the Mealy machine in VHDL and simulate it with Cypress NOVA simulator.

2) Simulate the state machine shown in Figure 3-8 with VHDL and describe what it does (Hint: See next question).

- 3) Design a Mealy state machine that computes the remainder of value 5 instead 3. Draw the state diagram and simulate it with VHDL. Test the machine using input 3, 4, 5, 6, 76, and 101.

- 4) Design the state machine of the state flow diagram in Figure 3-9 and the output table in Table 3-3.

| Table 3 | 3-3. |

|---------|------|

|---------|------|

| State / Output | OE | GO | ACT |

|----------------|----|----|-----|

| IDLE           | 0  | 0  | 0   |

| DECODE         | 0  | 0  | 0   |

| BUSY           | 0  | 0  | 1   |

| XFER           | 1  | 1  | 1   |

| XFER2          | 1  | 0  | 1   |

## 4. Digital Device Modeling

## 4.1 Introduction

Several VHDL concepts have been addressed in the previous lessons. VHDL topics covered in the previous lessons are various digital circuit modeling methodologies: structural, behavioral, and dataflow models. In addition to digital modeling, the text also covered the implementation of two types of state machines: Moore and Mealy state machines using the VHDL *process* statement. The *Process* statement is a unique feature in comparison to conventional imperative programming languages such as C, Pascal, FORTRAN, Ada, C++, etc. Due to the concurrent nature of VHDL programming, *Process* blocks execute/simulate in parallel. Statements inside of the *process* block, on the other hand, are executed sequentially. Parallel simulation is important because real world digital systems operate and behave in parallel. In the following lesson, this same concept of parallel executing *process* blocks will be addressed again. The emphasis here will be more towards the solving of real world application problems such as digital component modeling.

## 4.2 SRAM Memory

Memory plays an important role in the advancement of modern computers. When design a computing system, different types of memory are hierarchically structured into layers according to their data handling speed. The CPU is usually the fastest component and it is surrounded by various levels of memory. The various types of memory work in conjunction with the CPU: for example, on-chip and off-chip memory, memory chips surround the CPU on the motherboard, hard disk memory, and secondary memory device such as tape backups. To make computer efficient so the CPU will not be bogged down by the slower memory, different speeds of memory need to be used. Memory used by CPU are classified in general as SRAM (static RAM) and DRAM (dynamic RAM). SRAM memory runs faster than DRAM, and it interfaces directly with the CPU or the CPU on chip memory such as the L1 cache of the system. DRAM, on the other hand, is slower than SRAM by an order and requires more control circuitry, but has the advantages of smaller cell size and lower cost.

DRAM memory is denser than SRAM due to its circuit simplicity. Unlike SRAM which uses flip flops, DRAM stores information in capacitors, and information will only be kept until the charges in the capacitors leak out. As a consequence, more effort is needed to design DRAM "refresh circuitry" to preserve the stored DRAM information. Refreshing DRAM means re-charging the capacitors.

SRAM memory is much simpler to use than DRAM because it does not require a "refresh" operation. A generalized SRAM timing diagram is shown in Figure 4-1. SRAM is an asynchronous device. Read and write operations depend on the chip's selecting signal *nce* shown in Figure 4-1. Typical timing parameters found in an SRAM data book include signal *nce* to various signal edges, which also shown in Figure 4-1.

The SRAM signals shown in Figure 4-1 are described in Table 4-1. The signal type entry in the table describes the signal direction attribute such as input, output or bidirectional. The line *bidata* is set to high impedence when it is not used. By doing so, *bidata* will not cause data line conflict.

Timing parameters for an SRAM are also illustrated in Figure 4-1. They are the minimum times starting from the signal *nce* to various signals and they are the same for both read and write operations. Signal *nwrite* indicates read or write operation. If the SRAM is in write mode, *bidata* will be the input for capturing data. Oppositely, if the SRAM is in read mode, *bidata* will be used to output data.

Table 4-1. SRAM Signal Description

| Signal Name | Signal Type | Signal Description                  |  |

|-------------|-------------|-------------------------------------|--|

| NCE         | IN          | Not chip select signal.             |  |

| NWrite      | IN          | Not chip write or chip read signal. |  |

| Address     | IN          | Use for read and write address.     |  |

| Data        | IN/OUT      | Use for data input and data output. |  |

## 4.3 VHDL SRAM Memory Design

SRAM modeling can be implemented using the above timing information and previous VHDL lessons. A VHDL program that models a 2 bit by 4 word SRAM device is listed in Section 4.4. This program was compiled and simulated using the Cypress Warp tool. The simulation waveform is shown in Figure 4-2. From the figure, it can be seen that the data value 2 was written into the memory location 3 (*bidata*(1)='1' and *bidata*(0)='0') and read back afterwards.

Several VHDL concepts were used in this program. The first is the use of the *generic* statement. The *Generic* statement is similar to constant declaration in programming languages except it is more useful

due to the hardware design application. Notice that we have discussed a VHDL method for declaring constants in earlier lessons. *Generic* statement is different because it specifies where those constant are valid. In other words, the *generic* statement defines the scope of its constants. The *Generic* statement is to be used inside of an *entity* statement (see previous lessons), and the architecture body associated with this entity will be able to see and use these generic constants. It is a very powerful concept because it allows generalized hardware modeling. In the SRAM example, the size of the SRAM does not need to be fixed at 8 words deep and 2 bits per word. Different size SRAMs can be created by changing only the declaration inside of the *generic* statement.

The second concept is the use of the sub-program *procedure* statement. Although the *component* statement was introduced first, the *procedure* statement is the preferred construct due to its simplicity. The component structure is very much the same as the architecture structure. It uses an entity statement to specify input and output signals and an architecture body to define the relationship(s) of these signals. Declaration of a component is also needed in the main architecture body. As clear as the component concept may seem it, there are many hassles in creating and using *component* for simulation. Unless the *component* is useful or has already been created and put into a library, a *procedure* is the prefer choice.

Another reason why a *procedure* construct is preferred over a *component* construct is for ease of understanding VHDL code. In general, VHDL code for structure modeling is less likely to be comprehended than the corresponding behavior modeling which is naturally associated with *procedure* statement. The fact that behavior modeling is easier to grasp was shown in the previous lesson where a D flip-flop was represented in different VHDL models.

The third concept is the use of library routines. The *use* statement can be found between the *entity* statement and *architecture* statement. Since the Cypress VHDL compiler is mainly geared towards hardware synthesis, the behavior modeling aspect of Cypress VHDL compiler is weak because it doesn't have good support for modeling a resistor. For example, in the SRAM modeling below, to multiplex bidirectional line, *bidata*, component tristate buffer, *bufoe*, from the Cypress library *rtlpkg* would have to be used.

## 4.4 SRAM VHDL Listing

```

-- Entity statement

-- Specifies input, output and bidirectional signals

-- Specifies

entity sram0 is

generic(

address_width : integer := 2; -- column address width

address_size : integer := 4;

word_width : integer := 2; -- word width

zero_word : bit_vector := "00" -- To nullify a memory

);

port(

address

: in bit_vector (address_width-1 downto 0);

nwrite

: in bit:

nce

: in bit:

bidata

: inout x01z_vector (word_width-1 downto 0)

):

end sram0;

use work.rtlpkg.all;

-- bufoe(x, oe, y, yfb): Three state buffer with feedback.

use work.int_math.all; -- See Cypress VHDL synthesis reference page 4-86

-- i2bv(i,w): converts integer i to w width binary

```

-- signal.-- bv2i(a): inverse of function i2bv

```

_____

```

architecture sram0arch of sram0 is

type memory\_elmt is array (address\_size downto 0) of bit\_vector (address\_width downto 0);

-- Read from the memory

procedure ReadMemory ( nce, nwrite: in bit; address: in bit\_vector (address\_width-1 downto 0); memory\_word: in memory\_elmt; dataout: out bit\_vector (word\_width-1 downto 0)) is

variable i, w: integer; variable addressi: integer;

begin

end ReadMemory;

-- Write to the memory

```

-----

procedure WriteMemory

(nce, NWrite: in bit;

Address: in bit_vector (address_width-1 downto 0);

memory_word: out memory_elmt;

datain: in bit_vector (word_width-1 downto 0)) is

variable i, w: integer;

variable addressi: integer;

begin

if (nce='0') and nce'event then

if (nwrite='0') then

addressi := bv2i(address);

for i in 0 to address_size-1 loop

if(i=addressi) then

for w in 0 to word_width-1 loop

memory_word(i)(w) <= datain(w);</pre>

end loop;

end if;

end loop;

end if;

end if;

end WriteMemory;

```

\_\_\_\_\_

-- Main program

```

signal datain, dataout: bit_vector (word_width-1 downto 0);

signal memory_word: memory_elmt;

signal w: integer;

beain

-- Memory read cycle

process (nce)

begin

ReadMemory(nce, nwrite, address, memory_word, dataout);

end process;

-- Memory write cycle

process (nce)

begin

WriteMemory(nce, nwrite, address, memory_word, datain);

end process;

-- Tristate input and output

bif0: bufoe port map(dataout(0), nwrite, bidata(0), datain(0)):

bif1: bufoe port map(dataout(1), nwrite, bidata(1), datain(1));

```

end sram0arch;

Listing 4-1. SRAM VHDL Code

#### 4.5 Problems

- 1) The Cypress Warp tool uses the time unit tick. Figure 4-2 shows an example of tick value 68. From Figure 4-1, use the Warp simulator to determine the minimum times for signals  $T_{nce2datain}$ ,  $T_{nce2nwr}$  and  $T_{nce2data}$  that produce a valid  $T_{nce2dataout}$ . Also, what is the value of  $T_{nce2dataout}$ ?

- 2) The timing diagram in Figure 4-3 below shows a modified SRAM that contains an extra field for storing a valid bit. This memory is to be named SRAMvc (SRAM with valid control) memory. To put data into a memory location, the signal *nvalid* has to be set to zero prior to signal *nce*'s going during the SRAMvc reading cycle, if the signal *nvalid* at the requested address location is high, *bidata* should output zero. During the SRAMvc writing cycle, data will write into the memory along with the *nvalid* signal. If the signal *nvalid* is high, the maximum data value (all bits set to one) should write into the corresponding memory location.

Before using SRAMvc, a signal *nreset* should be applied to invalidate signal *nvalid* all memory locations (for example, *nvalid*<='0'). In result, all *nvalid* bits will be set to zero, and all *bidata* value will be set to max. See Figure 4-3 for the timing relationship of *nreset* and *nce*.

Construct SRAMvc using VHDL and prove its functional by simulation. The simulator should produce timing waveforms similar to those shown in Figure 4-3.

From the simulation, find all the timing parameters in Figure 4-3 based on the simulation of your SRAMvc VHDL model.

## 5. Digital Design using Divide and Conquer

## 5.1 Introduction

As the demand for digital system complexity increases, one needs to rely on traditional divide and conquer methodologies for constructing complex digital systems. VHDL contains features that support the divide and conquer technique for designing complex system design.

Some of the VHDL features that that permit the designer to build sub-systems have already been introduced in previous lessons: for example, the use of VHDL *component* block and *procedure* and *functions* statements. In addition, there is a benefit to breaking a large problem into many smaller problems because the solution for each small problem can be reused and applied to other problems similar in nature. For example, the design of an automobile fuel mixer controller might require the use of a two stage 5 bit D flip flop. By coincidence, this same odd device (2-stages, 5-bit D flip flop) is also used inside traffic light controller. One can imagine that the design for this device should not have to be implemented twice, provided the design tool (I.e. VHDL) allows it. This is the concept of hardware reuse, and for a long time it has been employed in the *object oriented* software world. In this lesson, the VHDL *package* and *library* between which support "hardware reuse" will be introduced.

## 5.2 VHDL features

The use of VHDL *component* and *procedure* statements in previous lessons gave the VHDL designer a systematic way of breaking a large and complicated problem into smaller, and simpler problems to solve. The VHDL *package* clause feature lets the digital designer pack tested digital parts into a library (storage). Then, he/she can use the VHDL keyword *use* or *library* to retrieve these parts for any design afterwards. This enables designer to build more complex systems and also encourages the digital design divide and conquer methodologies.

## 5.3 ALU Functions

The Arithmetic logic unit (ALU) is the most important part of the computation engine because it directly affects the system performance. All computational arithmetic or logic operations are done in the ALU. Therefore, it is clear that ALU output latency will affect the overall input to output delay. Figure 5-1 shows the general block diagram of an ALU.

The types of functions built into an ALU depends on the nature of computation. For example, a number crunching ALU such as a digital signal processor (DSP) will devote a good portion of ALU resources for floating point number manipulation such as floating point add, multiply, etc. An intelligent embedded

controller, on the other hand, would probably have an overall balanced arithmetic and logic functions, with emphasis on integer manipulation.

There are many ways to construct an ALU. During the 1980's, when Large Scale Integration (LSI) Integrated Chip (IC) and Medium Scale Integration IC were popular, bit-slice ALU design was the main technology due to its modularity for LSI and MSI design. The bit-slice design concept was used because it reduced computations to individual bits as to minimize each bit's overlapping functionality. In the current trend of integrated circuit technology (e.g. VLSI), ALU designers focus less on the ALU's bit versatility and more towards the its overall speed performance. An ALU design example is shown in Figure 5-2.

Figure 5-2 is a simplified ALU design, nevertheless, it shows a good overall ALU structure. In the ALU, function boxes, F0, F1, to Fn are dedicated for specified ALU functions such as add, multiply, shift, etc. The inputs to each function box are delivered by two buses, operand1 and operand2. Output of each function box is tapped onto the output bus via tri-state buffers. In addition to the resulting data outputs, there are also ALU flag outputs such as divide by zero, arithmetic overflow, underflow, etc. Each function box is controlled by the control input bits. When functions are similar in nature, for example, left circular and right circular shifts, control bits are used to distinguish these functions.

There are many arithmetic and logic functions that a computer architecture designer might like to put into an ALU. However, due to design requirements and technology limitations the designer must compromise all the factors for an optimal area and speed tradeoff.

## 5.4 ALU Component Implementation Examples

For simple laboratory work, one might like to design a 4-bit, 2's complement ALU which consists a 4-bit adder for integer arithmetic, left circular shift, right circular shift, and bitwise AND and OR logic functions.

VHDL supports modular hardware implementation by using the objected oriented software concept of reusability. In VHDL, code or program pieces such as a *procedure*, *function* or *component* can be stored into a *library* for later use. Whenever the parts are needed, they can be linked into the main VHDL program and reused again. The VHDL feature that supports part reuse is called *Package*, and it is described in the ALU implementation example.

## 5.4.1 Ripple Carry Adder Implementation

A ripple carry adder is the simplest adder and it is easiest to build. To implement a 4-bit adder, one starts by paralleling a half adder with full adders. Ripple carry adder implementation can be found in many digital design text books. this laboratory, half adder and full adder components were implemented and

they have been placed inside of the library, *Arith\_parts\_pkg package*. The listing of the *Arith\_parts\_pkg package* is shown in Section 5.4.2.

In *Arith\_parts\_pkg*, components half\_adder and full\_adder were combined to produce a 4-bit ripple carry adder *ripp\_adder4*. One example of hardware reuse is to test the functionality of *ripp\_adder4* without reimplementing the same module. This is done by creating a VHDL module, *addtest.vhd*, which is listed in Section 5.4.3. In file *addtest.vhd*, after the *entity* declaration, the line beginning with the VHDL key word *use* tells the VHDL compiler that all modules (*procedure*, *function*, and *component*) inside of the package *iarith\_parts\_pkg* are visible to file *addtest.vhd* and therefore are available for use.

Only the module *ripp\_adder4* is used structurally inside of the *addtest* module. Remaining modules such as *full\_adder* and *half adder* are not shown inside of the *addtest* module; nevertheless, they were important in building the ripple carry adder *ripp\_adder4*. The test wave form which illustrates the adder's functionality is shown in Figure 5-3. In Figure 5-3, *ain* is set to "1111" and *bin* is set to "0011". The output *aout* becomes "0010" with the overflow flag set to 1. Notice the glitches on the at *aout* lines caused by the asynchronous *ain* and *bin* input signals.

| Nova: ADDTEST Device: C375                 |                               |         |

|--------------------------------------------|-------------------------------|---------|

| <u>F</u> ile <u>E</u> dit <u>S</u> imulate | <u>V</u> iews <u>O</u> ptions | F1=Help |

| 22 ain_0                                   |                               | 1       |

| 99 ain_1                                   |                               |         |

| 139 ain_2                                  |                               |         |

| 39 ain_3                                   |                               |         |

| 45 aout_0                                  | ΩΩ                            |         |

| 43 aout_1                                  |                               |         |

| 58 aout_2                                  |                               |         |

| 103 aout_3                                 |                               |         |

| 19 bin_0                                   |                               |         |

| 59 bin_1                                   |                               |         |

| 102 bin_2                                  | 504 OF                        |         |

| 138 bin_3                                  |                               |         |

| 49 ovf                                     |                               |         |

|                                            |                               |         |

|                                            |                               | +       |

| <b>+</b>                                   |                               |         |

Figure 5-3. Ripple Carry Adder Waveform

## 5.4.2 Package *Iarith\_parts\_pkg* Listing

package iarith\_parts\_pkg is

component half\_adder port(signal Ain, Bin: in bit; signal Cout, Sout: out bit); end component; component full\_adder port(signal Cin, Ain, Bin: in bit;

```

signal Cout, Sout: out bit);

end component;

component ripp_adder4

port(signal Ain, Bin: in bit_vector (3 downto 0);

signal Sout: out bit_vector (3 downto 0);

signal OverFlow: out bit);

end component;

end iarith_parts_pkg;

_____

-- Half adder component

entity half_adder is

port(signal Ain, Bin: in bit;

signal Cout, Sout: out bit);

end half_adder;

architecture half_adder_arch of half_adder is

begin

process (Ain, Bin)

begin

if Ain='1' and Bin='1' then

Sout <= '0';

Cout <= '1';

else

Cout <= '0';

Sout <= Ain or Bin;

end if;

end process;

end half_adder_arch;

_____

-- Full adder component

entity full_adder is

port(signal Cin, Ain, Bin: in bit;

signal Cout, Sout: out bit);

end full_adder;

architecture full_adder_arch of full_adder is

begin

process (Ain, Bin, Cin)

begin

if Ain='1' and Bin='1' and Cin='1' then

Sout <= '1';

Cout <= '1';

elsif Cin='0' then

if Ain='1' and Bin='1' then

Sout <= '0';

Cout <= '1';

else

Sout <= Ain or Bin;

Cout <= '0';

end if;

else -- Cin='1' and either Ain='1' or Bin='1'

Sout <= not (Ain or Bin);

Cout <= Ain or Bin;

end if;

```

end process; end full\_adder\_arch;

-----

-- 4 bit adder component entity ripp\_adder4 is port(signal Ain, Bin: in bit\_vector (3 downto 0); signal Sout: out bit\_vector (3 downto 0); signal OverFlow: out bit); end ripp\_adder4; architecture ripp\_adder4\_arch of ripp\_adder4 is signal Cout: bit\_vector (3 downto 1); begin ha0: half\_adder port map(Ain=>Ain(0), Bin=>Bin(0), Cout=>Cout(1), Sout=>Sout(0)); fa1: full\_adder port map(Cin=>Cout(1), Ain=>Ain(1), Bin=>Bin(1), Cout=>Cout(2), Sout=>Sout(1)); fa2: full\_adder port map(Cin=>Cout(2), Ain=>Ain(2), Bin=>Bin(2), Cout=>Cout(3), Sout=>Sout(2)); fa3: full\_adder port map(Cin=>Cout(3), Ain=>Ain(3), Bin=>Bin(3), Cout=>OverFLow, Sout=>Sout(3));

end ripp\_adder4\_arch;

#### Listing 5-1. Iarith\_parts\_pkg VHDL Code Listing

### 5.4.3 Testadd.vhd Listing

-- to test ripple adder routine using component -- "ripp\_adder4" of vhdl file iar.vhd.

#### entity addtest is

generic( data\_wd: integer := 3);

port ( Ain: in bit\_vector (data\_wd downto 0); Bin: in bit\_vector (data\_wd downto 0); Aout:out bit\_vector(data\_wd downto 0); OVF: out bit);

end addtest;

#### use work.iarith\_parts\_pkg.all;

architecture addtest\_arch of addtest is

begin

op4: ripp\_adder4 port map(Ain, Bin, Aout, OVF);

end;

Listing 5-2. Testadd.vhd VHDL Code Listing

### 5.4.4 Circular Shifter Implementation

The circular shifter unit is more difficult to implement than simple bitwise logical operations. To make the implementation more challenging, the shifter was implemented in generalized fashion so it could accommodate various bus widths. Again, by applying the concept of reuse, the implementation of the circular shifter was put into a library for test. The library that contains the shifter is called *logic\_parts\_pkg*, and the VHDL code is listed in Section 5.4.6. Again, the testing of circular shift logic can be performed similar to the ripple carry adder test. The trace file for doing two right circular shifts on *ain* bits "0010" is "1000" and is shown in the Section 5.4.5. Notice that the output "1000" took 3 ticks to come out after applying inputs *ain* and *bin. Ain* is the bit to be shifted and *bin* is the shifted value. In the *cshift* component of *logic\_parts\_pkg*, input bit *RL* was used to indicate shift direction: RL='0' for left circular shift.

#### 5.4.5 Circular Shift Trace Data

NOVA Simulation Printout File: TEST.psd - View: PINS and REGS Printout produced: Thu Jun 13 01:46:57 1996 bbaaaaaaaa i i i i i i o o o o nnnnnuuuu t t t t  $\overline{1}$   $\overline{0}$   $\overline{1}$   $\overline{2}$   $\overline{3}$ 0 1 2 3 . . . . . . . 0: 0 1 0 0 1 0 L L L L 1: 0 1 0 0 1 0 L L L L 2:010010LLL 3: 0 1 0 0 1 0 H L L L 4: 0 1 0 0 1 0 H L L L 5:010010HLLL 6: 0 1 0 0 1 0 H T, T, T, 7:010010HLLL 8:010010HLLL 9:010010HLLL 10: 0 1 0 0 1 0 H L L L 11: 0 1 0 0 1 0 H L L L 12: 0 1 0 0 1 0 H L L L 13: 0 1 0 0 1 0 H T, T, T, 14: 0 1 0 0 1 0 H L L L

Listing 5-3. Circular Shift Trace Listing

#### 5.4.6 Package *Logic\_parts\_pkg* Listing

package logic\_parts\_pkg is component cshift

generic (data\_wd: integer:= 3);

port (Ain: in bit\_vector (data\_wd downto 0); Sin: in bit\_vector (1 downto 0); RL : in bit; Sout: out bit\_vector(data\_wd downto 0));

end component;

component bAND port (Ain: in bit\_vector (3 downto 0); Bin: in bit\_vector (3 downto 0); Cout: out bit\_vector (3 downto 0));

Digital Design VHDL Laboratory 5.Digital Design using Divide and Conquer pepe, 4/30/96

end component;

```

component bOR

port (Ain: in bit_vector (3 downto 0);

Bin: in bit_vector (3 downto 0);

Cout: out bit_vector (3 downto 0));

```

\_\_\_\_\_

end component;

end logic\_parts\_pkg;

-- Use Cypress library

use work.bv\_math.all; use work.int\_math.all;

-- Circular right or left shift

-- Input:

---

-- Ain - Input bits

-- Sin - Number of shift

- -- RL 0: left circular shift

- -- 1: right circular shift

- -- Output:

- -- Sout Output bits

-----

#### entity cshift is

generic(data\_wd: integer := 3);

port( Ain: in bit\_vector (data\_wd downto 0); Sin: in bit\_vector (1 downto 0); RL : in bit; Sout: out bit\_vector(data\_wd downto 0));

end cshift;

architecture cshift\_arch of cshift is

signal temp: bit\_vector (data\_wd downto 0); begin

process (Ain, Sin, RL) variable i, j, k, l: integer := 0; begin

-- i is the shifted value

for i in 0 to data\_wd loop

if i=bv2i(Sin) then

for j in 0 to data\_wd loop

-- Find right circular shift index k

if RL='1' then k := j+(data\_wd+1)-i;

-- Find left circular shift index k

else k := j+i; end if; -- Assign Output

```

if k > data_wd then

k := k-(data_wd+1);

end if;

```

for I in 0 to data\_wd loop if k=I then temp(I) <= Ain(j); end if; end loop;

end loop;

end if;

end loop;

Sout <= temp;

end process;

end cshift\_arch;

-----

-- Bitwise AND

entity bAND is port( Ain: in bit\_vector (3 downto 0); Bin: in bit\_vector (3 downto 0); Cout: out bit\_vector (3 downto 0));

end bAND;

architecture bAND\_arch of bAND is begin

process (Ain, Bin) begin Cout(3 downto 0) <= Ain(3 downto 0) and Bin(3 downto 0); end process;

end bAND\_arch;

end bOR\_arch;

#### Listing 5-4. Logic\_parts\_pkg VHDL Code Listing

# 5.5 ALU Implementation Example

Using components from Section 5.4 and the block diagram in Figure 5-2, one should be able effortlessly to construct an ALU. See the ALU VHDL code in Listing 5-5.

| use work.logic_parts_pkg.all;<br>use work.iarith_parts_pkg.all;                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| alu_comp                                                                                                                                                                                                                                                 |

| <br>Input:<br><br>Ain, Bin - Input bits<br>sel_bit - Calculation type selection bit<br>0001 - Bitwise AND operation                                                                                                                                      |

| <ul> <li>0010 - Bitwise AND operation</li> <li>0100 - Left circular shift</li> <li>0101 - Right circular shift</li> <li>1000 - Integer add.</li> </ul>                                                                                                   |

| Output:                                                                                                                                                                                                                                                  |